🍀🌼🌼🌼🌼🌼🌼🌼🍀

Dear students,

Welcome and have a nice day! In this session we will deal with flip flops, which is part of our PY1644 course as per CBCSS Physics syllabus (2014 revision) of Kerala University.

For better view of the scripted lectures, please click on the images one by one.

Learn in Lockdown with AKPCTA

Telegram Class at http://t.me/PY1644

(26/04/2020)

In the last session, we had studied the logic gates and combinational logic circuits in detail. For those who missed it, I provide the link of that session below, please go through it.

Coming to this session, we discuss the next type of logic circuits and their elements. In fact, logic circuits are of two types. Combinational logic circuits and sequential logic circuits. ഇതിൽ combinational logic circuits നെ സംബന്ധിച്ച് കഴിഞ്ഞ സെഷനിൽ നാം പഠിച്ച് കഴിഞ്ഞു. അതിന്റെ ലിങ്ക് കൊടുത്തിട്ടുണ്ട്. ബേസിക് ലോജിക് ഗേറ്റുകളായ AND, OR, NOT എന്നിവയുടെ combination നിലൂടെ ഇത് സാധ്യമാക്കാവുന്നതാണ്.

എന്നാൽ, sequential logic circuit കൾ timing and memory devices ആണ്. ഇവ flip flop കളാൽ നിർമ്മിതമാണ്. Flip flops എന്നാൽ bistable logic circuits ആണ്.

എന്തു കൊണ്ടാണ് flip flops ഒരു memory element ആകുന്നത് എന്ന വസ്തുത മനസ്സിലാക്കിയിട്ട് വേണം വിവിധ തരം flip-flops നെ സംബന്ധിച്ചും ഓരോന്നിന്റെയും പ്രവർത്തനത്തേയും നേട്ടത്തേയും കോട്ടത്തേയും ആസ്പദമാക്കിയൊക്കെ പഠിയ്ക്കാൻ .

നമുക്കറിയാം ഡിജിറ്റൽ സാങ്കേതിക വിദ്യയിൽ ഡാറ്റാ സൂക്ഷിക്കപ്പെടുന്നത് ബിറ്റുകളുടെ രൂപത്തിലാണ്. Binary digital technology ആണ് നാം കൈകാര്യം ചെയ്യുന്നതെങ്കിൽ, നമുക്കറിയാം അവിടെ രണ്ട് ബിറ്റുകൾ മാത്രമാണുള്ളത്. അവ 1 ഉം 0 വും ആണ്. ഈ ഒന്നിന്റേയും പൂജ്യത്തിന്റേയും പല permutations and combinations വഴി നമുക്ക് വിവരങ്ങൾ ഡാറ്റകൾ ആയി സൂക്ഷിക്കാം.

ഉദാഹരണത്തിന്, 8 എന്ന decimal number ന് തുല്യമായ binary data 1000 ആണ് . അതുപോലെ, 10 ന് തുല്യമായത് 1010 ആണന്നും നമുക്കറിയാം. ഒരു flip flop binary രൂപത്തിലുള്ള രണ്ട് outputs തരുമെന്നിരിയ്ക്കെ, രണ്ട് flip-flop കളെ ഒരു sequential രീതിയിൽ arrange ചെയ്ത് സർക്യൂട്ടാക്കിയാൽ, അവയുടെ ഔട്ട്പുട്ടുകൾ മേൽ സൂചിപ്പിച്ച നമ്പറുകൾക്ക് സമാനമായ ബൈനറി ബിറ്റുകളുടെ ക്രമത്തിൽ രൂപപ്പെടുത്തുക വഴി ഡാറ്റാ സ്റ്റോറേജ് സാധ്യമാകുന്നു എന്ന് വളരെ പ്രാഥമികമായി അനുമാനിയ്ക്കാം. Registers നെ സംബന്ധിധിച്ച് പഠിയ്ക്കുമ്പോഴെ അത് കൂടുതൽ വിശദമാക്കാൻ സാധിക്കു. ഇൻപുട്ട് കണ്ടീഷനുകളിൽ വേണ്ട മാറ്റങ്ങൾ വരുത്തി ഔട്ട്പുട്ട് ബിറ്റുകളെ വേണ്ട ക്രമത്തിൽ രൂപപ്പെടുത്താൻ സാധിക്കുമെന്നതാണ് ഓരോ flip-flop ന്റേയും പ്രത്യേകത.

ഇങ്ങനെ സ്റ്റോർ ചെയ്യപ്പെടുന്ന ഡാറ്റാ എത്ര സമയം വരെ സൂക്ഷിക്കണമെന്നും എപ്പോൾ change ചെയ്യണമെന്നും തീരുമാനിയ്ക്കുന്നത് input state കളും previous output state കളും സംയുക്തമായിട്ടാണ്. Input state കളുടെ നിയന്ത്രണം user ടെ കൈവശമാണങ്കിൽ, user requirements അനുസരിച്ച്

previous out put states നെയും ആസ്പദമാക്കി ഡാറ്റാ store ചെയ്യപ്പെടും. ചില flip flop കളിൽ input data യ്ക്ക് മുകളിൽ ഒരു clock pulse വഴിയും out put state നെ നിർണ്ണയിക്കാൻ സാധിക്കും. അത്തരം ഘട്ടങ്ങളിൽ clock pulse മായി input ഉം previous output ഉം synchronous ചെയ്താൽ മാത്രമേ പുതിയ out put states നെ നിർണ്ണയിക്കാൻ സാധിക്കുള്ളു. പ്രാഥമികമായി ഇത്രയും കാര്യങ്ങൾ മനസ്സിലാക്കി വേണം വിശദമായ പഠനത്തിലേയ്ക്ക് കടക്കാൻ.

Bistable elements ൽ ഉൾപ്പെടുന്നവയാണ്

Latches. NAND gates മാത്രമായി ഉപയോഗിച്ചും അല്ലങ്കിൽ NOR gates മാത്രമായി ഉപയോഗിച്ചും latches design ചെയ്യാം. രണ്ടിടത്തും രണ്ട് വീതം ഗേറ്റുകൾ ഉപയോഗിക്കുന്നുണ്ട്. സ്ക്രിപ്റ്റിലെ ചിത്രങ്ങൾ പരിശോധിച്ചാൽ വ്യക്തമാകും.

ഒരു സർക്യൂട്ടിലെ രണ്ട് ഗേറ്റുകളുടേയും ഔട്ട്പുട്ട് ആദ്യം സെറ്റ് ചെയ്യുന്നു (by some means). അതേ പോലെ ഓരോ ഗേറ്റിലേയും ഒര് ഇൻപുട്ടും സെറ്റ് ചെയ്യുന്നു ( R & S)! ഓരോ ഗേറ്റിന്റേയും രണ്ടാമത്തെ ഇൻപുട്ട് ആയി രണ്ട് ഗേറ്റുകളുടേയും നിലവിലെ ഔട്ട് പുട്ടിനെ പരസ്പരം exchange change ചെയ്ത് കൊടുക്കുന്നു ( ചിത്രം പരിശോധിയ്ക്കുക). തുടർന്ന്, ഓരോ ഗേറ്റിലേയും രണ്ട് ഇൻപുട്ടുകളും ലോജിക് ഓപ്പറേഷനുകൾക്ക് വിധേയമായി (NAND / NOR) പുതിയ ഔട്ട് പുട്ടുകൾ (SET (1) & RESET (0)) നൽകുന്നു. ഈ പ്രക്രിയ തുടരുന്നതിനനുസരിച്ച് latches നിരന്തരം ഔട്ട് പുട്ടുകൾ നൽകി കൊണ്ടേ ഇരിയ്ക്കും.

ചുരുക്കത്തിൽ, പുതിയ ഇൻപുട്ട് കണ്ടീഷനുകൾക്കും നിലവിലെ ഔട്ട് പുട്ടിനും വിധേയമായി ഔട്ട് പുട്ട് മാറ്റമില്ലാതെ തുടരുകയോ, മാറ്റങ്ങൾക്ക് വിധേയമാകുകയോ ചെയ്യാം! അതുകൊണ്ട് തന്നെ ഇവയെ ഒരു മെമ്മറി ഡിവൈസ് ആയി ഉപയോഗിയ്ക്കാം . ഈ ആശയം ഉപയോഗിച്ച്, latches ന്റെ ലോജിക് സർക്യൂട്ടും ട്രൂത്ത് ടേബിളും വ്യക്തമായി മനസ്സിലാക്കുക.

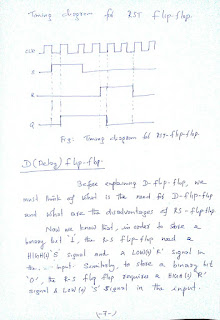

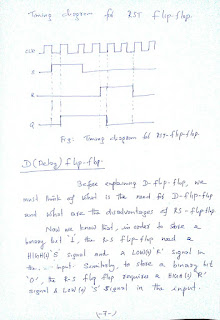

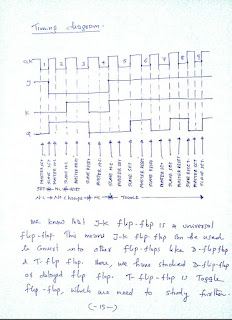

Initial input condition ആയ R=0, S=0 ഇവ വീണ്ടും ആവർത്തിക്കണമെന്നില്ല. ഒരു latch നു സമാനമായിത്തന്നെയാണ് RS flip flops function ചെയ്യുന്നത്. അവയുടെ timing diagram സ്ക്രിപ്റ്റിൽ നിന്നും മനസ്സിലാക്കുക! Timing diagram എന്നാൽ ഒരു truth table ന്റെ graphical representation ആണ്. Timing diagram ത്തിൽ നിന്നും ഈ bistable device ന്റ രണ്ട് stable outputs ആയ HIGH (1) & LOW (0) കിട്ടാനുള്ള input conditions വ്യക്തമാണ്. ഒരു NAND latch RS flip-flop നെ സംബന്ധിച്ചിടത്തോളം, output ൽ 1 എന്ന binary bit ആണ് store ചെയ്യേണ്ടതെങ്കിൽ , ഇൻപുട്ടിൽ R=0, S=1 എന്ന് സെറ്റ് ചെയ്യണം. അതേപോലെ, 0 ആണ് ഔട്ട്പുട്ടിൽ സ്റ്റോർ ചെയ്യേണ്ടതെങ്കിൽ, ഇൻപുട്ടിൽ R= 1, S= 0 എന്നും സെറ്റ് ചെയ്യണം.

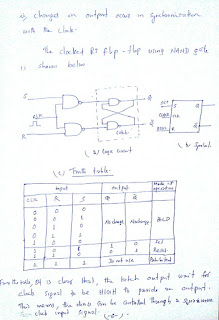

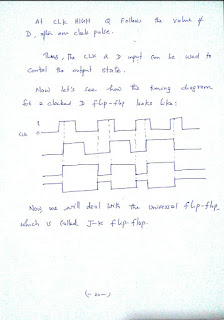

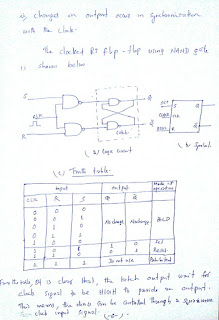

Synchronous അഥവാ clocked RS Flip flop ലേയ്ക്ക് വരുമ്പോൾ, തൊട്ട് മുൻപേ പ്രതിപാദിച്ച asynchronous or unclocked RS flip flop ൽ നിന്നും വ്യത്യസ്തമായി ഒരു square wave clock pulse input (CLK) അധികമായി വരുന്നു! Clock pulse HIGH ആകുന്ന condition നിൽ മാത്രമേ ഈ flip flop ഉപയോഗത്തിനായി പ്രവർത്തന സജ്ജമാകു! ഇൻപുട്ടിലെ മാറ്റങ്ങൾ ഔട്ട് പുട്ടിൽ പ്രതിഫലിപ്പിക്കണമെങ്കിൽ ഒരു Complete clock pulse പൂർത്തീകരിയ്ക്കുക്കുന്നതിന്റെ സമയമെടുക്കും. Logic diagram, symbol, truth table, timing diagram എന്നിവ script ൽ നിന്നും മനസ്സിലാക്കുക!

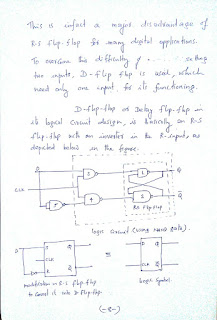

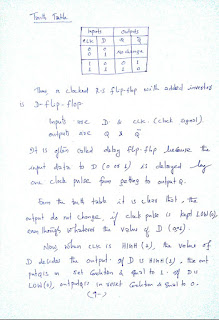

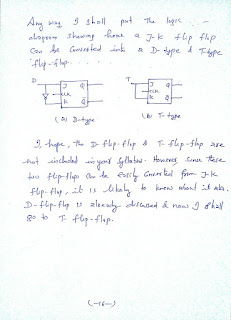

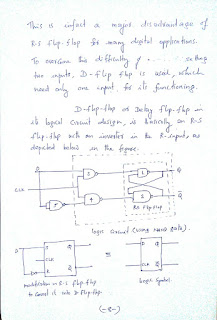

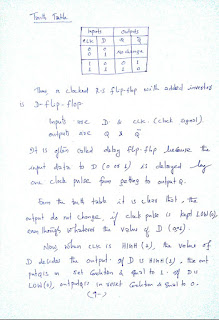

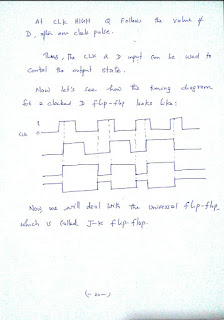

RS flip flop ന്റെ ഒരു പ്രധാന കോട്ടം, ഔട്ട് പുട്ടിൽ ഒരു binary bit സ്റ്റോർ ചെയ്യാൻ രണ്ട് ഇൻപുട്ട്കൾ സെറ്റ് ചെയ്യണമെന്നതാണ് . അതെങ്ങനെയാണന്ന് നാം നേരത്തെ വിശദീകരിച്ചു. ഈ പോരായ്മ പരിഹരിച്ചു കൊണ്ട് പുതിയ ഒരു flip flop പരിചയപ്പെടുത്തുന്നു; അതിന്റെ പേരാണ് D flip flop അഥവാ Delay flip-flop. ഇവിടെ clock pulse കൂടാതെ ഒരു ഇൻപുട്ടിന്റെ ആവശ്യമേ വരുന്നുള്ളു, ആ ഇൻപുട്ടിനെ D ഇൻപുട്ട് എന്നും വിളിയ്ക്കുക്കുന്നു. Script ൽ നിന്നും D flip-flop ന്റെ logic diagram, logic symbol, truth table, timing diagram എന്നിവ വ്യക്തമായി മനസ്സിലാക്കുക!

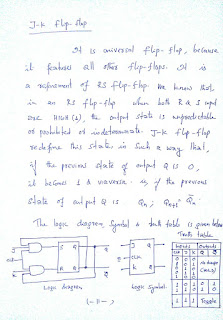

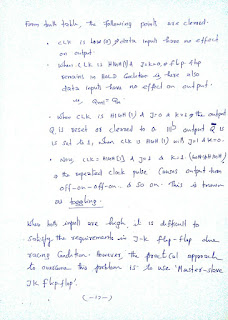

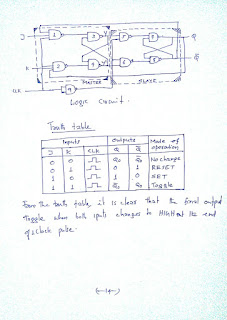

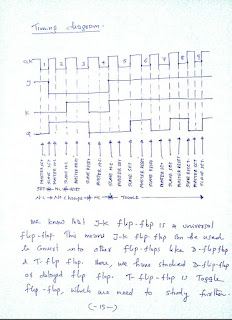

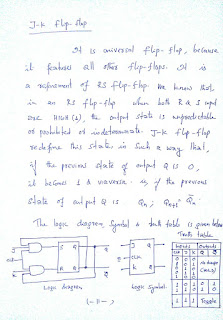

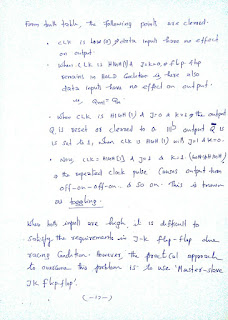

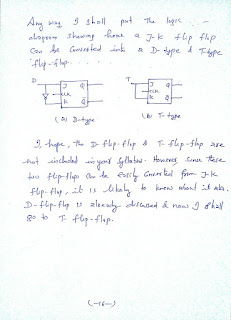

ഇനി നാം പോകുന്നത്, universal flip flop എന്നറിയപ്പെടുന്ന JK flip flop ലേയ്ക്കാണ്. അങ്ങനെ അറിയപ്പെടാൻ കാരണം JK flip flop മറ്റെല്ലാ flip flop കളുടേയും സവിശേഷതകൾ ഉൾക്കൊള്ളുന്നവ ആയതിനാലാണ്. ഈ flip flop നെ ഒരു RS refined or redefined flip flop എന്നും പറയാം. ഈ flip flop ൽ നിന്നും D flip flop ലേയ്ക്കും , ഇനി പഠിയ്ക്കാൻ പോകുന്ന T flip flop ലേയ്ക്കും വളരെ എളുപ്പത്തിൽ മാറാം. R=S=1 എന്ന input condition, ഒരു RS flip-flop ന്റെ output നെ പ്രവചനാതീതമാക്കുമ്പോൾ, J=K=1 എന്ന input condition (clock pulse HIGH), JK flip flop ൽ output വ്യക്തമായി നൽകുന്നു. ആ output തൊട്ട് മുൻപത്തെ state ലെ output ന് complement (toggle) ഉം ആയിരിയ്ക്കും. അതായത് RS flip-flop ലെ unpredictable state നെ JK flip-flop , redefine ചെയ്യുന്നു എന്ന് സാരം. Script ൽ, logic diagram, logic symbol, truth table എന്നിവ കൃത്യമായും സ്പഷ്ടമാവും നൽകിയിട്ടുണ്ട്. അവ ഇപ്പോൾ നൽകിയ വിശദീകരണത്തിന്റെ അടിസ്ഥാനത്തിൽ മനസ്സിലാക്കി പഠിയ്ക്കുക!

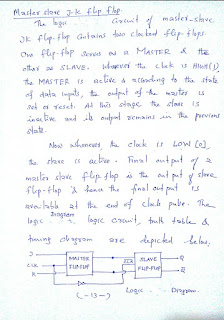

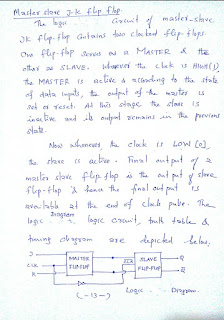

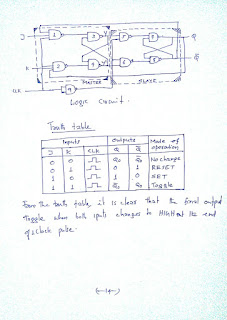

അടുത്തതായി Master-Slave JK flip flop ആണ്. ഇവിടെ, രണ്ട് clocked JK flip-flop കളിൽ ഒന്ന് Master ആയും മറ്റേത് Slave ആയും വർത്തിയ്ക്കുന്നു. Clock input HIGH ആകുമ്പോൾ Master ഉം LOW ആകുമ്പോൾ slave ഉം active ആകുന്നു. ഒരു clock pulse ന്റെ അവസാനം, final output , slave flip-flop ന്റെ output ൽ ലഭിയ്ക്കുന്നു. Input condition നുകൾക്ക് വിധേയമായി SET (1), RESET(0), toggle എന്നീ output കൾ ലഭിയ്ക്കുന്നു. Logic diagram, logic circuit, truth table, timing diagram എന്നിവ ഇവിടെ വിവരിച്ചതിന്റെ വെളിച്ചത്തിൽ script വായിച്ച് മനസ്സിലാക്കി പഠിയ്ക്കുക.

T flip-flop എന്നാൽ toggle flip flop എന്നാണ്. D flip flop നെ പ്പോലെ clock pulse കൂടാതെ ഒരൊറ്റ input മാത്രമേ T flip flop നുള്ളു ! Input മാറുന്നതിന് അനുസരിച്ച് output toggle ചെയ്യുന്നു. അതായത്, output തൊട്ടു മുന്നത്തെ state ന്റെ output ന് നേർ complement ആയിരിയ്ക്കും. Logic diagram, symbol, truth table, input-output wave form ഇവ കൃത്യമായി script ൽ ഉൾപ്പെടുത്തിയിട്ടുണ്ട്. Waveform ൽ top square wave നെ T (input) എന്നും താഴെയുള്ളവയെ Q, Qcomplement (out puts) എന്നും യഥാക്രമം വായിക്കുക!

വിവിധ flip flop കളുടെ ഒരു സംക്ഷിപ്ത രൂപം ചുവടെ ചേർക്കുന്നു.

Thank you for being here. We will see again with another session of lectures regarding the semiconductor memory devices. Till then bye!

🌲🌲🌲🌲🌲🌲🌲🌲🌲🌲🌲🌲